May 2024 - Jul. 2024

Synopsis¶

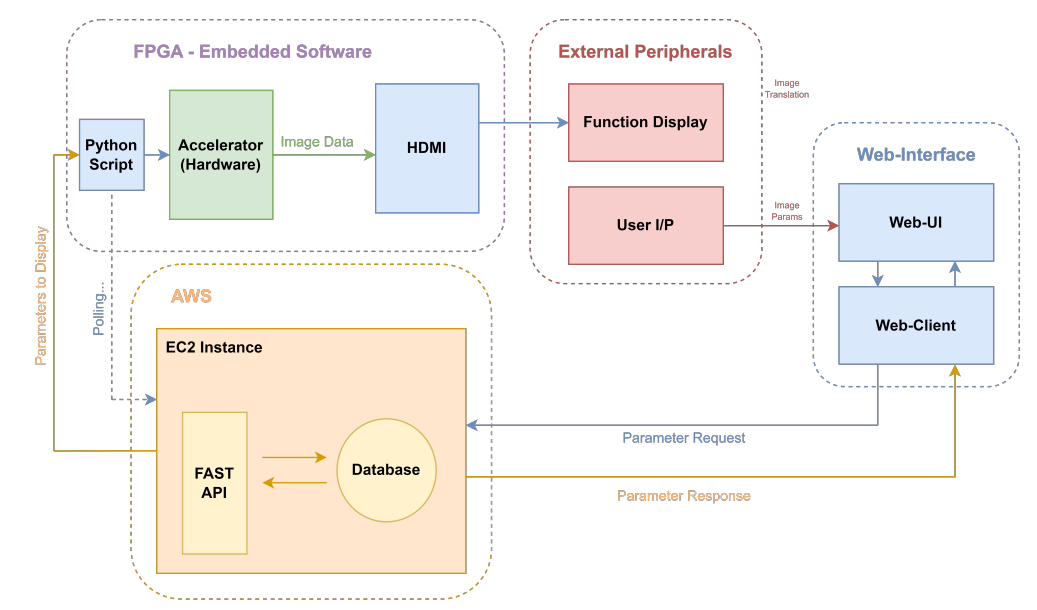

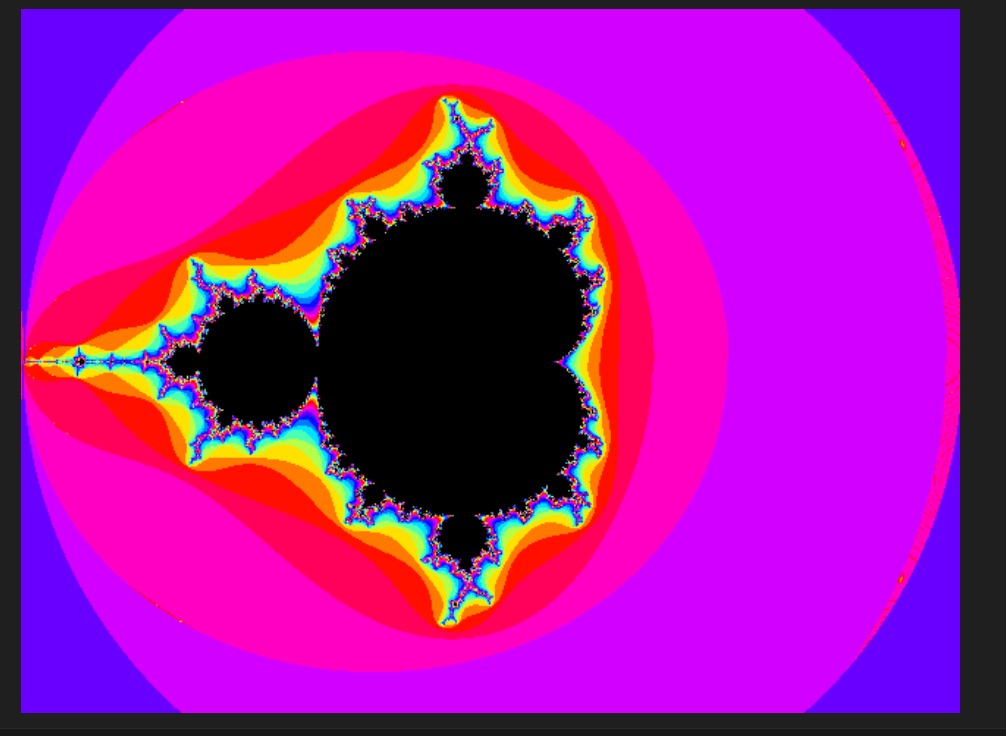

For the 2nd year, end-of-year project we were tasked with designing and developing an educational tool to visualise mathematical functions. Our solution was an IoT system including a web front-end, a server-side database and a mathematical accelerator synthesised on a PYNQ-Z1 FPGA. I was responsible for developing an ESP32 UI in MicroPython, a software implementation of the fractal visualisation and a concurrent client Python program to interface with an AWS server, FPGA register file and HDMI output. I was also responsible for testing the solution based on project requirements. Additionally I was involved in the debugging of the accelerator, described in SystemVerilog and Verilog.

Skills¶

Below are the skills and experiences gained from the project:

Competencies with MicroPython, Cython, SystemVerilog, Verilog and Python, including libraries: asyncio, websockets, requests, numpy and panda

Competency using Vivado

Competency using GitHub for collaborative development

Experience with FPGA development and workflow

Experience working in a team